Stato supporto MT3620

Questo documento descrive lo stato corrente del supporto di Azure Sphere per MediaTek MT3620. Puoi anche fare riferimento al documento breve sul prodotto MT3620, disponibile per il download nella pagina Web MediaTek MT3620. Inoltre, MediaTek produce il manuale dell'utente relativo all'hardware MT3620, che è una guida dettagliata per l'integrazione della MCU MT3620 nel proprio hardware.

Importante

Nel contesto di questo documento, attualmente non supportato significa che l'uso della caratteristica da parte del cliente è limitato al momento e questa restrizione sarà probabilmente rimossa in futuro. Al contrario, non accessibile significa che la funzionalità non può essere usata dai clienti e che è improbabile che questa restrizione cambi.

Se hai richieste di funzionalità o feedback, i tuoi commenti sono benvenuti nel forum della community di Azure Sphere.

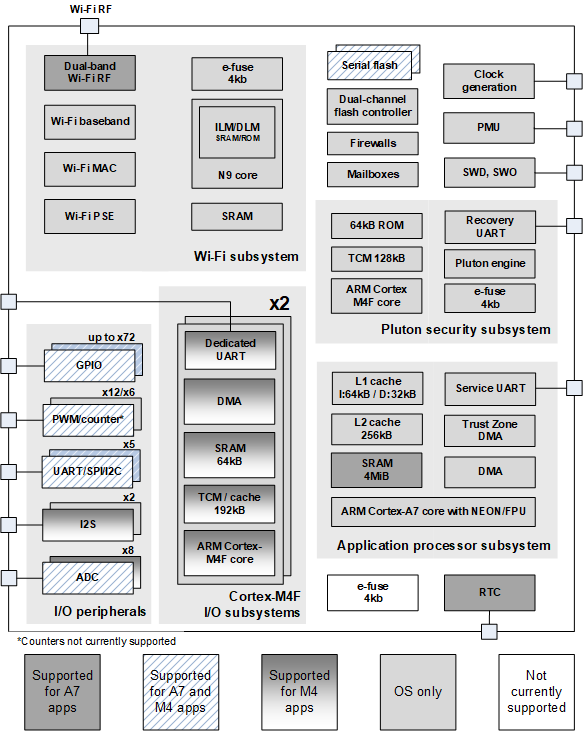

Diagramma a blocchi MT3620

Il diagramma a blocchi mostra il supporto fornito per ogni componente MT3620. Le sezioni che seguono il diagramma forniscono ulteriori dettagli su questi componenti.

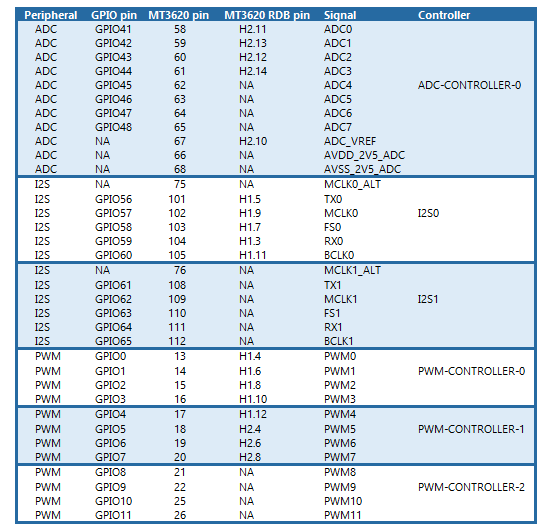

Periferiche di I/O

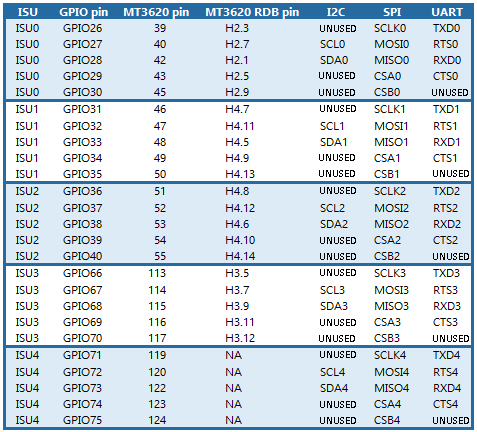

Il design MT3620 include un totale di 76 pin di I/O programmabili. Come illustrato nelle due tabelle seguenti, la maggior parte dei pin è multiplexata tra I/O generico (GPIO) e altre funzioni. Oltre ai pin GPIO elencati, GPIO12-23 sono disponibili rispettivamente sui pin MT3620 27-38.

Facendo riferimento alla tabella seguente, i pin contrassegnati come "INUTILIZZATI" non vengono utilizzati dalla periferica ISU associata e possono essere configurati per l'uso come pin GPIO.

Nota

Una volta allocata una periferica ISU a un core, tutti e 5 i pin ISU, inclusi i pin inutilizzati, sono limitati all'uso in tale core.

GPIO/PWM/contatori

Alcuni pin sono multiplexed tra GPIO, frequenza di compressione della larghezza di impulso (PWM) e contatori hardware.

Le funzioni GPIO attualmente supportate impostano input di lettura e high/low. Sono supportati anche modalità di scaricamento/open source di guida aperte e controllo della forza di guida. Gli interrupt esterni sono supportati nel core M4 ma non nel core A7.

L'MT3620 ha 12 canali PWM, identificati da PWM0-PWM11. Sono organizzati in 3 gruppi di 4 canali. Ogni gruppo è associato a un controller PWM (PWM-CONTROLLER-0, PWM-CONTROLLER-1, PWM-CONTROLLER-2). I canali PWM e GPIO bloccano la mappa da GPIO0 a GPIO11 agli stessi pin nell'MT3620. Se l'applicazione utilizza un controller PWM, tutti i pin associati a tale controller vengono allocati per l'uso come output PWM e nessuno di essi può essere utilizzato per GPIO.

L'hardware PWM può essere configurato per utilizzare una delle tre frequenze a clock fisso: 32 KHz, 2 MHz (XTAL/13) o 26 MHz (XTAL). Sui core in tempo reale (RT), un'applicazione in tempo reale (RTApp) può selezionare l'orologio da utilizzare come base. Nel core di alto livello (A7), il driver Linux userà sempre l'orologio a 2 MHz. Ciò si traduce in duty cycle e periodo limitazioni in applicazioni di alto livello, come spiegato in Utilizzare PWA nelle applicazioni di alto livello.

Blocchi ISU (Serial Interface)

Il design MT3620 include cinque blocchi di interfaccia seriali, ognuno dei quali contiene cinque pin. (Questi blocchi sono chiamati anche ISU, per "I2C, SPI, UART.") Questi blocchi di interfaccia seriali possono multiplex GPIO, UART (Universal Asynchronous Receiver-Transmitter), I2C (Inter-Integrated Circuit) e SPI (Serial Peripheral Interface).

UART è supportato in 1200, 2400, 4800, 9600, 19200, 38400, 57600, 115200, 230400, 460800, 500000, 576000, 921600, 1000000, 1152000, 1500000 e 2000000 baud. Esiste un buffer di ricezione hardware a 32 byte. Sono supportate le impostazioni UART seguenti, con 8N1 (8 bit di dati, 1 bit di interruzione e nessuna parità) come impostazione predefinita:

- Bit di dati: 5, 6, 7 e 8.

- Bit di arresto: 1 e 2.

- Parità: dispari, pari e nessuno.

- Modalità controllo flusso: RTS/CTS, XON/XOFF e nessun controllo di flusso.

Le transazioni SPI sono supportate fino a 40 MHz. È possibile connettere fino a due dispositivi SPI subordinati a ogni ISU. Quando si utilizza una porta ISU come interfaccia master SPI, non è possibile usare la stessa porta di un'interfaccia I2C o UART. Le operazioni SPI bidirezionali simultanee (full-duplex) in una singola transazione bus non sono supportate. Sono supportate le impostazioni SPI seguenti:

- Modalità di comunicazione (polarità orologio, fase orologio): modalità SPI 0 (CPOL = 0, CPHA = 0), modalità SPI 1 (CPOL = 0, CPHA = 1), modalità SPI 2 (CPOL = 1, CPHA = 0) e modalità SPI 3 (CPOL = 1, CPHA = 1).

- Ordine di bit: il minimo significativo viene inviato per primo e il più significativo viene inviato per primo.

- Polarità di selezione chip: attivo-alto, attivo-basso. Attivo-minimo è l'impostazione predefinita.

Gli indirizzi di dispositivi subordinati a 7 bit sono supportati per I2C. Gli indirizzi subordinati I2C a 8 o a 10 bit non sono supportati. Quando si utilizza una porta ISU come interfaccia master I2C, non è possibile usare la stessa porta di un'interfaccia SPI o UART. Le letture I2C a 0 byte non sono supportate. Sono supportate le impostazioni I2C seguenti:

- Velocità bus da 100 KHz, 400 KHz e 1 MHz.

- Timeout personalizzato per le operazioni.

I2S

Due blocchi di cinque pin sono multipli tra GPIO e I2S.Two blocks of five pins are multiplexed between GPIO and I2S. I2S è attualmente supportato solo per le applicazioni M4.

ADC

Mt3620 contiene un ADC a 12 bit con 8 canali di input. Un blocco di otto pin viene multiplexato tra GPIO e ADC. I canali di input ADC e GPIO bloccano la mappa da GPIO41 a GPIO48 agli stessi pin sull'MT3260. Tuttavia, se l'applicazione usa ADC, tutti gli 8 pin vengono allocati per l'uso come input ADC e nessuno di essi può essere utilizzato per GPIO.

Sottosistemi ARM Cortex-M4F

Mt3620 include due sottosistemi ARM Cortex-M4F di uso generale, ognuno dei quali ha un blocco GPIO/UART dedicato.

Mt3620 supporta una frequenza di clock predefinita di 26 MHz. Tuttavia, ogni core M4 può essere configurato in modo indipendente per funzionare a qualsiasi frequenza di clock tra 1 MHz e 200 MHz impostando il suo registro HCLK_CK_CTRL. Il codice seguente illustra un modo per impostare la frequenza di clock su 200 MHz:

volatile unsigned int *hclk_ck_ctrl = (unsigned int *)0x2101000c;

*hclk_ck_ctrl = 0x00040200;

Nota

Per informazioni dettagliate sulla programmazione dei core M4 su MT3620, vedi la documentazione mt3620 pubblicata da MediaTek. Se il foglio dati non contiene tutte le informazioni necessarie, inviare un messaggio di posta elettronica a Avnet (Azure.Sphere@avnet.com) per richiedere l'intero foglio dati.

I sottosistemi ARM Cortex-M4F possono essere programmati per supportare gli interrupt esterni. Per informazioni dettagliate, vedere Usare interrupt esterni in applicazioni in tempo reale .

Sottosistema processore applicazione

Il sottosistema ARM Cortex-A7 esegue un'applicazione del cliente insieme al kernel, ai servizi e alle librerie basati su Linux forniti da Microsoft.

Il servizio UART è dedicato alla funzionalità di sistema per il sottosistema A7. Non è disponibile per l'uso delle applicazioni del cliente.

Il blocco e-fuse programmabile una tantum, per l'archiviazione di informazioni specifiche del dispositivo, non può essere utilizzato dalle applicazioni del cliente.

Sottosistema Wi-Fi

Il sottosistema Wi-Fi è attualmente conforme a IEEE 802.11 b/g/n sia a 2,4 GHz che a 5 GHz.

Attualmente Azure Sphere supporta solo WPA2, EAP-TLS e autenticazione aperta (senza password).

Vedi Strumenti di test RF per informazioni sui test e sulla calibrazione delle radiofrequenze.

Controllo dell'alimentazione

L'MT3620 include funzionalità di riduzione dell'alimentazione e profilo di alimentazione per controllare il consumo di energia. Per informazioni dettagliate, vedere Considerazioni su Power Down e Considerazioni sul profilo di risparmio energia.

Orologi e fonti di alimentazione

Il cristallo principale al momento può essere solo 26 MHz. Le frequenze a cristalli diverse da 26 MHz non sono attualmente supportate nel software.

Rilevamento brownout

Il rilevamento dei brownout non è attualmente supportato.

Timer per il cane da guardia hardware

L'MTK3620 include diversi timer per cani da guardia:

- Un timer di cane da guardia dedicato per l'uso da parte del dominio di sicurezza DiNon. Questo timer del cane da guardia non è disponibile per l'uso da parte delle applicazioni.

- Un timer di cane da guardia disponibile per il processore applicazione. Il sistema operativo Azure Sphere utilizza questo timer per il cane da guardia per i servizi di sistema. Questo timer del cane da guardia non è disponibile per le applicazioni.

- Un timer da guardia per ognuno dei core in tempo reale. Questi timer di cane da guardia sono disponibili per le applicazioni in tempo reale.

Per altre informazioni, vedi Usare un timer per il cane da guardia in una RTApp .

SWD, SWO

Il debug tramite cavo seriale (SWD, pin 98-99) è supportato solo per le applicazioni M4. L'uscita con cavo seriale (SWO, pin 100) non è attualmente supportata. Il debug di un'applicazione A7 è supportato da un meccanismo basato su gdb fornito da Microsoft.

RAM e flash

L'MT3620 include circa 5 MB di RAM al die, di cui 256 KiB in ogni sottosistema I/O e 4 MB nel sottosistema dell'applicazione A7.

L'MT3620 può essere ordinato con 16 MB di memoria flash SPI.

Per informazioni su RAM e flash disponibili per le applicazioni, vedi Memoria disponibile per le applicazioni.

Supporto per i test di produzione

Documentazione e utilità per supportare l'integrazione di applicazioni di test di produzione personalizzate con processi di produzione non sono ancora disponibili.

Pinout

| Spilla# | Aggiungi nome | Funzioni principali | Digitare | Descrizione | Commenti |

|---|---|---|---|---|---|

| 1 | GND | P | Terra | ||

| 2 | AVDD_3V3_WF_A_PA | PI | Rail di alimentazione da 3,3 V per amplificatore di potenza Wi-Fi 5 GHz | ||

| 3 | AVDD_3V3_WF_A_PA | PI | Rail di alimentazione da 3,3 V per amplificatore di potenza Wi-Fi 5 GHz | ||

| 4 | NC | ||||

| 5 | NC | ||||

| 6 | AVDD_1V6_WF_TRX | PI | Binario di alimentazione da 1,6 V per Wi-Fi trasmissione/ricezione | ||

| 7 | AVDD_1V6_WF_AFE | PI | Binario di alimentazione da 1,6 V per Wi-Fi front-end analogico | ||

| 8 | NC | ||||

| 9 | AVDD_1V6_XO | PI | Binario di alimentazione da 1,6 V per oscillatore a cristallo principale | ||

| 10 | MAIN_XIN | AI | Ingresso dell'oscillatore di cristallo principale | ||

| 11 | WF_ANTSEL0 | FARE | Wi-Fi selezione dell'antenna per l'interruttore DPDT esterno | ||

| 12 | WF_ANTSEL1 | FARE | Wi-Fi selezione dell'antenna per l'interruttore DPDT esterno | ||

| 13 | GPIO0 | GPIO0/PWM0 | DIO | Multiplo GPIO che supporta l'interrupt con output PWM | |

| 14 | GPIO1 | GPIO1/PWM1 | DIO | Multiplo GPIO che supporta l'interrupt con output PWM | |

| 15 | GPIO2 | GPIO2/PWM2 | DIO | Multiplo GPIO che supporta l'interrupt con output PWM | |

| 16 | GPIO3 | GPIO3/PWM3 | DIO | Multiplo GPIO che supporta l'interrupt con output PWM | |

| 17 | GPIO4 | GPIO4/PWM4 | DIO | Multiplo GPIO che supporta l'interrupt con output PWM | |

| 18 | GPIO5 | GPIO5/PWM5 | DIO | Multiplo GPIO che supporta l'interrupt con output PWM | |

| 19 | GPIO6 | GPIO6/PWM6 | DIO | Multiplo GPIO che supporta l'interrupt con output PWM | |

| 20 | GPIO7 | GPIO7/PWM7 | DIO | Multiplo GPIO che supporta l'interrupt con output PWM | |

| 21 | GPIO8 | GPIO8/PWM8 | DIO | Multiplo GPIO che supporta l'interrupt con output PWM | |

| 22 | GPIO9 | GPIO9/PWM9 | DIO | Multiplo GPIO che supporta l'interrupt con output PWM | |

| 23 | DVDD_1V15 | PI | Binario di alimentazione da 1,15 V | ||

| 24 | DVDD_3V3 | PI | Binario di alimentazione da 3,3 V | ||

| 25 | GPIO10 | GPIO10/PWM10 | DIO | Multiplo GPIO che supporta l'interrupt con output PWM | |

| 26 | GPIO11 | GPIO11/PWM11 | DIO | Multiplo GPIO che supporta l'interrupt con output PWM | |

| 27 | GPIO12 | DIO | GPIO che supporta l'interrupt | Gli interrupt non sono attualmente supportati | |

| 28 | GPIO13 | DIO | GPIO che supporta l'interrupt | Gli interrupt non sono attualmente supportati | |

| 29 | GPIO14 | DIO | GPIO che supporta l'interrupt | Gli interrupt non sono attualmente supportati | |

| 30 | GPIO15 | DIO | GPIO che supporta l'interrupt | Gli interrupt non sono attualmente supportati | |

| 31 | GPIO16 | DIO | GPIO che supporta l'interrupt | Gli interrupt non sono attualmente supportati | |

| 32 | GPIO17 | DIO | GPIO che supporta l'interrupt | Gli interrupt non sono attualmente supportati | |

| 33 | GPIO18 | DIO | GPIO che supporta l'interrupt | Gli interrupt non sono attualmente supportati | |

| 34 | GPIO19 | DIO | GPIO che supporta l'interrupt | Gli interrupt non sono attualmente supportati | |

| 35 | GPIO20 | DIO | GPIO che supporta l'interrupt | Gli interrupt non sono attualmente supportati | |

| 36 | GPIO21 | DIO | GPIO che supporta l'interrupt | Gli interrupt non sono attualmente supportati | |

| 37 | GPIO22 | DIO | GPIO che supporta l'interrupt | Gli interrupt non sono attualmente supportati | |

| 38 | GPIO23 | DIO | GPIO che supporta l'interrupt | Gli interrupt non sono attualmente supportati | |

| 39 | GPIO26 | GPIO26/SCLK0/TXD0 | DIO | GPIO multiplo con funzioni ISU 0 | |

| 40 | GPIO27 | GPIO27/MOSI0/RTS0/SCL0 | DIO | GPIO multiplo con funzioni ISU 0 | |

| 41 | GND | P | Terra | ||

| 42 | GPIO28 | GPIO28/MISO0/RXD0/SDA0 | DIO | GPIO multiplo con funzioni ISU 0 | |

| 43 | GPIO29 | GPIO29/CSA0/CTS0 | DIO | GPIO multiplo con funzioni ISU 0 | |

| 44 | DVDD_1V15 | PI | Binario di alimentazione da 1,15 V | ||

| 45 | GPIO30 | GPIO30/CSB0 | DIO | GPIO multiplo con funzioni ISU 0 | |

| 46 | GPIO31 | GPIO31/SCLK1/TXD1 | DIO | GPIO multiplexed with ISU 1 functions | |

| 47 | GPIO32 | GPIO32/MOSI1/RTS1/SCL1 | DIO | GPIO multiplexed with ISU 1 functions | |

| 48 | GPIO33 | GPIO33/MISO1/RXD1/SDA1 | DIO | GPIO multiplexed with ISU 1 functions | |

| 49 | GPIO34 | GPIO34/CSA1/CTS1 | DIO | GPIO multiplexed with ISU 1 functions | |

| 50 | GPIO35 | GPIO35/CSB1 | DIO | GPIO multiplexed with ISU 1 functions | |

| 51 | GPIO36 | GPIO36/SCLK2/TXD2 | DIO | GPIO multiplo con funzioni ISU 2 | |

| 52 | GPIO37 | GPIO37/MOSI2/RTS2/SCL2 | DIO | GPIO multiplo con funzioni ISU 2 | |

| 53 | GPIO38 | GPIO38/MISO2/RXD2/SDA2 | DIO | GPIO multiplo con funzioni ISU 2 | |

| 54 | GPIO39 | GPIO39/CSA2/CTS2 | DIO | GPIO multiplo con funzioni ISU 2 | |

| 55 | GPIO40 | GPIO40/CSB2 | DIO | GPIO multiplo con funzioni ISU 2 | |

| 56 | DVDD_3V3 | PI | Binario di alimentazione da 3,3 V | ||

| 57 | DVDD_1V15 | PI | Binario di alimentazione da 1,15 V | ||

| 58 | GPIO41 | GPIO41/ADC0 | DIO | GPIO multiplexed with ADC input | |

| 59 | GPIO42 | GPIO42/ADC1 | DIO | GPIO multiplexed with ADC input | |

| 60 | GPIO43 | GPIO43/ADC2 | DIO | GPIO multiplexed with ADC input | |

| 61 | GPIO44 | GPIO44/ADC3 | DIO | GPIO multiplexed with ADC input | |

| 62 | GPIO45 | GPIO45/ADC4 | DIO | GPIO multiplexed with ADC input | |

| 63 | GPIO46 | GPIO46/ADC5 | DIO | GPIO multiplexed with ADC input | |

| 64 | GPIO47 | GPIO47/ADC6 | DIO | GPIO multiplexed with ADC input | |

| 65 | GPIO48 | GPIO48/ADC7 | DIO | GPIO multiplexed with ADC input | |

| 66 | AVDD_2V5_ADC | PI | Binario di alimentazione da 2,5 V per ADC | ||

| 67 | VREF_ADC | AI | Tensione di riferimento per ADC | ||

| 68 | AVSS_2V5_ADC | P | Terreno per ADC | ||

| 69 | EXT_PMU_EN | FARE | L'alimentatore esterno abilita l'uscita | ||

| 70 | WAKEUP | DI | Riattivazione esterna dalla modalità di sospensione più profonda | Non attualmente supportato | |

| 71 | AVDD_3V3_RTC | PI | Binario di alimentazione da 3,3 V per orologio in tempo reale | ||

| 72 | RTC_XIN | AI | Ingresso dell'oscillatore di cristallo orologio in tempo reale | ||

| 73 | RTC_XOUT | AO | Output dell'oscillatore di cristallo dell'orologio in tempo reale | ||

| 74 | AVDD_3V3_XPPLL | PI | Binario di alimentazione da 3,3 V per circuito interno a circuito bloccato | ||

| 75 | I2S_MCLK0_ALT | AO | Alternativa analogica a MCLK0 | I2S è attualmente supportato solo per le applicazioni M4. | |

| 76 | I2S_MCLK1_ALT | AO | Alternativa analogica a MCLK1 | I2S è attualmente supportato solo per le applicazioni M4. | |

| 77 | DVDD_1V15 | PI | Binario di alimentazione da 1,15 V | ||

| 78 | DVDD_1V15 | PI | Binario di alimentazione da 1,15 V | ||

| 79 | VOUT_2V5 | PO | Output da LDO interno da 2,5 V | ||

| 80 | AVDD_3V3 | PI | Binario di alimentazione da 3,3 V | ||

| 81 | PMU_EN | DI | Override PMU interno | ||

| 82 | RISERVATI | ||||

| 83 | GND | P | Terra | ||

| 84 | SENSE_1V15 | AI | Sensore ingresso per stabilizzare l'alimentatore da 1,15 V | ||

| 85 | VOUT_1V15 | PO | Output da LDO interno da 1,15 V | ||

| 86 | AVDD_1V6_CLDO | PI | Binario di alimentazione da 1,6 V per l'LDO interno con nucleo da 1,15 V | ||

| 87 | PMU_CAP | Un | Collega un capacitore tra questo pin e AVDD_3V3_BUCK per mantenere la stabilità del PMU | ||

| 88 | AVDD_3V3_BUCK | PI | Binario di alimentazione da 3,3 V per convertitore CC-DC da 1,6 V | ||

| 89 | AVDD_3V3_BUCK | PI | Binario di alimentazione da 3,3 V per convertitore CC-DC da 1,6 V | ||

| 90 | VOUT_1V6 | PO | Uscita da convertitore buck da 1,6 V interno | ||

| 91 | VOUT_1V6 | PO | Uscita da convertitore buck da 1,6 V interno | ||

| 92 | AVSS_3V3_BUCK | P | Terreno per convertitore buck da 1,6 V interno | ||

| 93 | AVSS_3V3_BUCK | P | Terreno per convertitore buck da 1,6 V interno | ||

| 94 | DEBUG_RXD | DI | Riservato per il debug di Azure Sphere | ||

| 95 | DEBUG_TXD | FARE | Riservato per il debug di Azure Sphere | ||

| 96 | DEBUG_RTS | FARE | Riservato per il debug di Azure Sphere | ||

| 97 | DEBUG_CTS | DI | Riservato per il debug di Azure Sphere | ||

| 98 | SWD_DIO | DIO | ARM SWD for Cortex-M4F debug | ||

| 99 | SWD_CLK | DI | ARM SWD for Cortex-M4F debug | ||

| 100 | SWO | FARE | ARM SWO per debug Cortex-M4F | Non attualmente supportato | |

| 101 | GPIO56 | GPIO56/TX0 | DIO | GPIO multiplo con I2S 0 | I2S è attualmente supportato solo per le applicazioni M4. |

| 102 | GPIO57 | GPIO57 /MCLK0 | DIO | GPIO multiplo con I2S 0 | I2S è attualmente supportato solo per le applicazioni M4. |

| 103 | GPIO58 | GPIO58/FS0 | DIO | GPIO multiplo con I2S 0 | I2S è attualmente supportato solo per le applicazioni M4. |

| 104 | GPIO59 | GPIO59/RX0 | DIO | GPIO multiplo con I2S 0 | I2S è attualmente supportato solo per le applicazioni M4. |

| 105 | GPIO60 | GPIO60/BCLK0 | DIO | GPIO multiplo con I2S 0 | I2S è attualmente supportato solo per le applicazioni M4. |

| 106 | DVDD_1V15 | PI | Binario di alimentazione da 1,15 V | ||

| 107 | DVDD_3V3 | PI | Binario di alimentazione da 3,3 V | ||

| 108 | GPIO61 | GPIO61/TX1 | DIO | GPIO multiplo con I2S 1 | I2S è attualmente supportato solo per le applicazioni M4. |

| 109 | GPIO62 | GPIO62/MCLK1 | DIO | GPIO multiplo con I2S 1 | I2S è attualmente supportato solo per le applicazioni M4. |

| 110 | GPIO63 | GPIO63/FS1 | DIO | GPIO multiplo con I2S 1 | I2S è attualmente supportato solo per le applicazioni M4. |

| 111 | GPIO64 | GPIO64/RX1 | DIO | GPIO multiplo con I2S 1 | I2S è attualmente supportato solo per le applicazioni M4. |

| 112 | GPIO65 | GPIO65/BCLK1 | DIO | GPIO multiplo con I2S 1 | I2S è attualmente supportato solo per le applicazioni M4. |

| 113 | GPIO66 | GPIO66/SCLK3/TXD3 | DIO | GPIO multiplo con funzioni ISU 3 | |

| 114 | GPIO67 | GPIO67/MOSI3/RTS3/SCL3 | DIO | GPIO multiplo con funzioni ISU 3 | |

| 115 | GPIO68 | GPIO68/MISO3/RXD3/SDA3 | DIO | GPIO multiplo con funzioni ISU 3 | |

| 116 | GPIO69 | GPIO69/CSA3/CTS3 | DIO | GPIO multiplo con funzioni ISU 3 | |

| 117 | GPIO70 | GPIO70/CSB3 | DIO | GPIO multiplo con funzioni ISU 3 | Attualmente supporta solo GPIO |

| 118 | DVDD_3V3 | PI | Binario di alimentazione da 3,3 V | ||

| 119 | GPIO71 | GPIO71/SCLK4/TXD4 | DIO | GPIO multiplo con funzioni ISU 4 | |

| 120 | GPIO72 | GPIO72/MOSI4/RTS4/SCL4 | DIO | GPIO multiplo con funzioni ISU 4 | |

| 121 | DVDD_1V15 | PI | Binario di alimentazione da 1,15 V | ||

| 122 | GPIO73 | GPIO73/MISO4/RXD4/SDA4 | DIO | GPIO multiplo con funzioni ISU 4 | |

| 123 | GPIO74 | GPIO74/CSA4/CTS4 | DIO | GPIO multiplo con funzioni ISU 4 | |

| 124 | GPIO75 | GPIO75/CSB4 | DIO | GPIO multiplo con funzioni ISU 4 | |

| 125 | SYSRST_N | DI | Ripristino del sistema, attivo basso | ||

| 126 | DVDD_1V15 | PI | Binario di alimentazione da 1,15 V | ||

| 127 | SERVICE_TXD | FARE | Porta del servizio Azure Sphere | Non disponibile per l'uso delle applicazioni del cliente | |

| 128 | SERVICE_RTS | FARE | Porta del servizio Azure Sphere | Non disponibile per l'uso delle applicazioni del cliente | |

| 129 | SERVICE_RXD | DI | Porta del servizio Azure Sphere | Non disponibile per l'uso delle applicazioni del cliente | |

| 130 | SERVICE_CTS | DI | Porta del servizio Azure Sphere | Non disponibile per l'uso delle applicazioni del cliente | |

| 131 | RISERVATI | ||||

| 132 | DVDD_1V15 | PI | Binario di alimentazione da 1,15 V | ||

| 133 | DVDD_3V3 | PI | Binario di alimentazione da 3,3 V | ||

| 134 | RECOVERY_RXD | DI | Porta di ripristino azure sphere | Non disponibile per l'uso delle applicazioni del cliente | |

| 135 | RECOVERY_TXD | FARE | Porta di ripristino azure sphere | Non disponibile per l'uso delle applicazioni del cliente | |

| 136 | RECOVERY_RTS | FARE | Porta di ripristino azure sphere | Non disponibile per l'uso delle applicazioni del cliente | |

| 137 | RECOVERY_CTS | DI | Porta di ripristino azure sphere | Non disponibile per l'uso delle applicazioni del cliente | |

| 138 | IO0_GPIO85 | IO0_RXD IO0_GPIO85/. | DI | GPIO dedicato multixed con UART per I/O M4 0 | |

| 139 | IO0_GPIO86 | IO0_TXD IO0_GPIO86/. | FARE | GPIO dedicato multixed con UART per I/O M4 0 | |

| 140 | IO0_GPIO87 | IO0_RTS IO0_GPIO87/. | FARE | GPIO dedicato multixed con UART per I/O M4 0 | |

| 141 | IO0_GPIO88 | IO0_CTS/IO0_GPIO88 | DI | GPIO dedicato multixed con UART per I/O M4 0 | |

| 142 | IO1_GPIO89 | IO1_RXD IO1_GPIO89/. | DI | GPIO dedicato multixed con UART per I/O M4 1 | |

| 143 | IO1_GPIO90 | IO1_GPIO90/IO1_TXD | FARE | GPIO dedicato multixed con UART per I/O M4 1 | |

| 144 | DVDD_3V3 | PI | Binario di alimentazione da 3,3 V | ||

| 145 | IO1_GPIO91 | IO1_RTS IO1_GPIO91/. | FARE | GPIO dedicato multixed con UART per I/O M4 1 | |

| 146 | IO1_GPIO92 | IO1_GPIO92/IO1_CTS | DI | GPIO dedicato multixed con UART per I/O M4 1 | |

| 147 | RISERVATI | ||||

| 148 | TEST | DI | Deve essere tirato basso per il normale funzionamento | ||

| 149 | WF_G_RF_AUXIN | RF | 2,4 GHz Wi-Fi ricevere porta diversità | ||

| 150 | NC | ||||

| 151 | AVDD_3V3_WF_G_PA | PI | Rail di alimentazione da 3,3 V per amplificatore di potenza da 2,4 GHz Wi-Fi | ||

| 152 | NC | ||||

| 153 | WF_G_RF_ION | RF | Porta antenna (differenziale) Wi-Fi 2,4 GHz | ||

| 154 | WF_G_RF_ION | RF | Porta antenna (differenziale) Wi-Fi 2,4 GHz | ||

| 155 | WF_G_RF_IOP | RF | Porta antenna (differenziale) Wi-Fi 2,4 GHz | ||

| 156 | WF_G_RF_IOP | RF | Porta antenna (differenziale) Wi-Fi 2,4 GHz | ||

| 157 | NC | ||||

| 158 | AVDD_3V3_WF_G_TX | PI | Binario di alimentazione da 3,3 V per trasmissione di alimentazione Wi-Fi 2,4 GHz | ||

| 159 | WF_A_RF_AUXIN | RF | Porta di diversità di ricezione Wi-Fi 5 GHz | ||

| 160 | AVDD_3V3_WF_A_TX | PI | Binario di alimentazione da 3,3 V per trasmissione di alimentazione Wi-Fi 5 GHz | ||

| 161 | NC | ||||

| 162 | WF_A_RFIO | RF | Porta antenna Wi-Fi 5 GHz (non bilanciata) | ||

| 163 | WF_A_RFIO | RF | Porta antenna Wi-Fi 5 GHz (non bilanciata) | ||

| 164 | GND | P | Terra | ||

| 165 | EPAD | P | Terra |